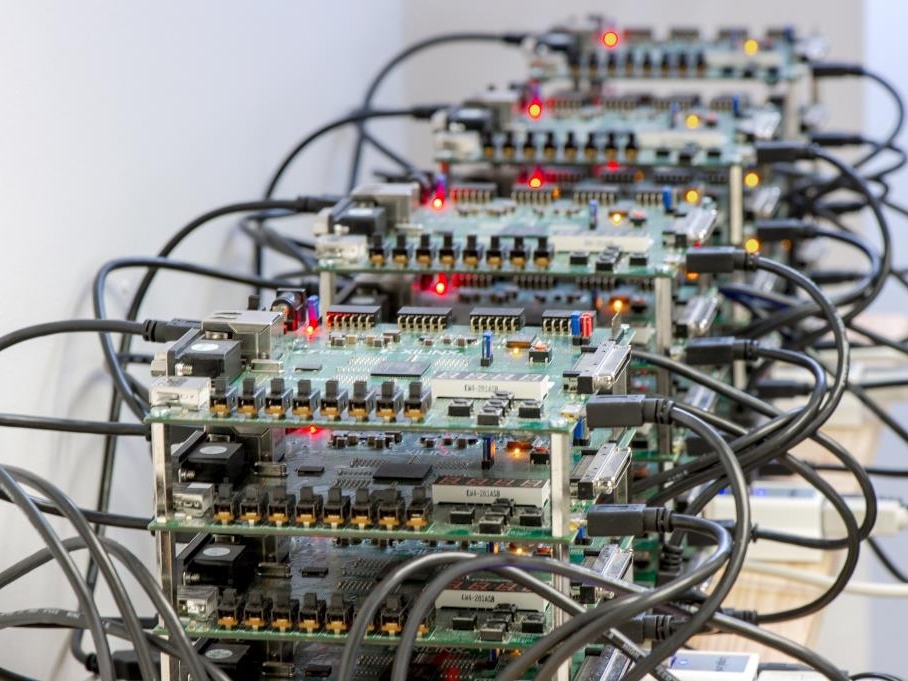

Die Herausforderung: Flexible und sichere FPGA-Systeme bauen. Rekonfigurierbare Hardwarebausteine, sogenannte FPGAs, ermöglichen die Beschleunigung von Netzwerkfunktionen. Ihre Programmierbarkeit erlaubt neue Flexibilität. Ein Vorteil, der auch Angriffsmöglichkeiten bietet. Für die IT-Sicherheit zeigt das: es braucht ein hohes Maß an Erfahrungswissen. Dieses Seminar stattet Sie damit aus. In einem Vorgespräch lassen sich die Inhalte des Seminars deshalb unternehmensspezifisch anpassen.

Absicherung FPGA-Basierter Systeme

Sicherheitsfeatures und Gegenmaßnahmen wirksam einsetzen

Die Herausforderung: Flexible und dennoch sichere FPGA-basierte Systeme bauen

FPGAs sind wertvolle Bausteine für eingebettete Systeme, da sie Hardware-Beschleunigung in Kleinserien ohne ASIC-Fertigung und Änderungen der Hardware im Einsatz ermöglichen.

Die wesentlichen Eigenschaften der FPGAs führen aber gleichzeitig zu neuen Angriffsmöglichkeiten und Schwachstellen. Moderne FPGAs bringen eine Vielzahl von Sicherheitsfunktionen mit, die zur Härtung richtig angewandt werden müssen.

Die Lösung: Integrierte FPGA Mechanismen kennen und sicher einsetzen

Das Seminar beinhaltet daher IT-Sicherheitsfragestellungen, die spezifisch für FPGAs sind. Ausgehend von dem Ziel, ein sicheres eingebettetes System mit einem integrierten FPGA-Chip zu designen, werden mögliche Angriffe, Schutzmaßnahmen kommerziell verfügbarer FPGAs und beispielhafte Sicherheitskonzepte behandelt.

Ihre Vorteile auf einen Blick

Nach dem Seminar können Sie …

- aktuelle Angriffe auf FPGAs und Sicherheitsprobleme beim Einsatz von FPGAs nachvollziehen

- Gegenmaßnahmen aktueller Chips verstehen und beispielhaft Sicherheitskonzepte kennenlernen, um sichere Systeme zu designen

Dieses Seminar bietet Ihnen …

- eine umfangreiche Schulung zu FPGA-basierten Angriffen, Problemen, Produkten und deren Features und Sicherheitsonzepten

- die Möglichkeit, sich mit Experten in FPGA-Sicherheit auszutauschen

- 06.06.2025 in Garching bei München (Anmeldung bis 22.05.2025)

- Das Seminar ist auf den Bedarf Ihres Unternehmens ausgerichtet, so dass der Inhalte und der Umfang in einem Vorgespräch unternehmensspezifischangepasst werden kann.

- Architekt*innen und Entwickler*innen für eingebettete Systeme

- Hardware-Architekt*innen und Entwickler*innen

- Technische Leitungen in Entwicklungsprojekten

- IT-Security Fachexpert*innen

- Einführung und Marktanalyse FPGA

- Angriffe auf FPGA

- Reverse Engineering

- Seitenkanalangriffe

- Fehlerangriffe

- Sicherheitskonzepte für FPGAs in Embedded Systemen

- FPGA Auswahlkriterien

Die Teilnehmenden erhalten einen Überblick der aktuellen Angriffe auf FPGAs und verstehen, welche Gegenmaßnahmen mit aktuellen Chips implementiert werden können, um ein sicheres System zu designen. Nach dem Seminar sind sie in der Lage, anhand von relevanten Kriterien, den geeigneten FPGA für die Absicherung ihres Systems auszuwählen.

Dr. Nisha Jacob Kabakci

Nisha Jacob Kabakci erhielt einen BEng. in Telekommunikation an der Visvesvaraya Technological University in Bangalore, Indien. Sie hat einen MSc. in Embedded Systems Design am Advanced Learning and Research Institute der Universität Lugano, Schweiz, abgeschlossen (in Zusammenarbeit mit der ETH Zürich und dem Politecnico di Milano). Während dieser Zeit arbeitete Frau Jacob in der Forschungsgruppe für Kodierung und Kryptographie an der Nanyang Technological University in Singapur mit Schwerpunkt auf der effizienten Implementierung von kryptographischen Kernen. Seit November 2012 arbeitet sie als wissenschaftliche Mitarbeiterin am Fraunhofer Institut für Angewandte und Integrierte Sicherheit (AISEC). Hier ist sie an der Entwicklung sicherer Lösungen für eingebettete Systeme und an Sicherheitsevaluationen auf Systemebene beteiligt. Ihre Forschungsschwerpunkte sind Hardware-Trojaner und FPGA-Sicherheit.